# Multi-core Debugger Integration and Suspend/Resume

Peter de Jager Intel Corporation

# **Copyright Permission**

A non-exclusive, irrevocable, royalty-free copyright permission is granted by Intel Corporation to use this material in developing all future revisions and editions of the resulting draft and approved Accellera Systems Initiative SystemC standard, and in derivative works based on the standard.

# Outline

- Background & Motivation

- Problem statement

- Previous solution & other approaches

- Synchronization control

- Generic applicability

- Generic simulation control

- Conclusion, Proposal & Discussion

# Background & Motivation

- About the author:

- Located @ Intel Eindhoven, Silicon Hive team

- Group develops tools (HiveLogic) to create cores and systems

- Technology has been used in a variety of products for a variety of application domains, including :

- video coding

- video post-processing

- imaging

- communications

### Silicon Hive technology: Four key elements

Design-time configurable processor & system architecture templates supported by elaborate libraries of hand-optimized, fully parameterized processor & peripheral building blocks

A unique methodology for fast & vast design space exploration at processor and system-level, supported by highly abstract design entry through high-level languages

A fully automated flow and corresponding tools for (multi-) processor & system hardware generation

|                                                                                                  | <ul> <li>I and Participation Control of the Control of the Control of the Control of Control of</li></ul> |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contractions                                                                                     | E. The second seco            |

|                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                  | لـــــلتان ر                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

A fully retargetable programming tool suite based on ANSI-C source entry

Slide courtesy of Jeroen Leijten, Sr. Principal Engineer, Intel Corporation

SYSTEMC<sup>™</sup> EVOLUTION DAY 0CT 28, 2021 | VIRTUAL WORKSHOP

# Background & Motivation

- Products that use our technology are

- Multi-core

- Heterogeneous

- Application-specific (dsp, vector, vliw, custom memories, ...)

- standard SystemC/TLM used as basis for System-Simulation technology

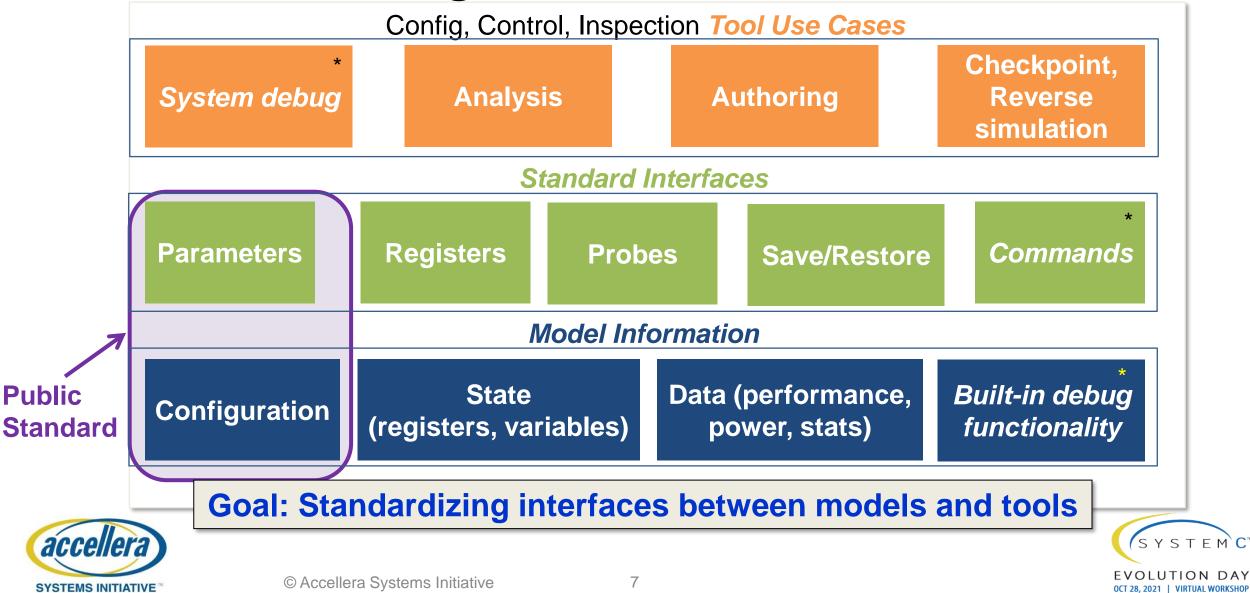

- A generic mechanism to support <u>application-software</u> debugging is not available in SystemC reference implementation and CCI 1.0

## Background & Motivation

### **Problem statement**

Systemsimulation with *n*-core models needs support for multi-core debugging

- REQ. 1 <u>MUST</u> be able to simultaneously connect {0..*n*} debug-connections, each to a separate core

- REQ. 2 MUST provide full (normal) debug functionality per attached debugger, irrespective of other debuggers being connected

- REQ. 3 MUST suspend system-simulation completely at end of current delta-cycle in case of

- Breakpoint hit (in application code, breakpoint set via debugger)

- Error triggered (due to application-code)

- User-break request (via debugger)

- REQ. 4 MUST resume system-simulation only when all attached debuggers have issued (or still are in) 'continue'-command

- REQ. 5 MUST suspend system-simulation when debug-connection is established during simulation

- REQ. 6 MUST remove debug-connection from current list of 'simulation blockers' when debug-connection is detached

- When number of 'simulation blockers' is 0, simulation shall resume

- REQ. 7 MUST be able to attach debugger when system in 'suspended'-state (due to other debug-connection)

- REQ. 8 MUST be able to user-break the 'continue'-command in a debugger when system in 'suspended'-state

- REQ. 9 MUST function with official SystemC (currently 2.3.3) distribution

- OPEN How to handle connections to/from other simulators? How do these 'see' that this part is 'suspended'?

RED: not supported with previous solution

### **Previous solution**

As discussed in presentation SystemC Evolution Day 2020

- Parallel debug-thread & simulation-thread

- Debug-thread uses boost::asio threads to handle multiple connections

- simulation-thread is locked on interrupt/user-break/bp-hit

- Per iss-model: quite complex handling of step/run commands with locks/mutexes/conditions

- When simulation-thread is locked, new connections & user-break in other debug-connection not possible (since that requires a reaction from the model)

- prohibits inspection of application code on other cores

### **Previous solution**

As discussed in presentation SystemC Evolution Day 2020

Conclusion last year:

- Move control on SystemC thread stop/continue into global DebugService handling the pausing/resuming of simulation

- Keep administration on corestates & debuggers

- Intercept userbreak when SystemC-thread is already stopped

- Continue only when all cores in 'broken'-state have received continue-command

# Other approaches

- (Un)Suspend(able) Mark burton, SCED-2019

- Proposes extension to SystemC api → breaks Req. 9

- sc\_suspend\_all(sim\_context)/sc\_unsuspend\_all(sim\_context)

- sc\_suspendable()/sc\_unsuspendable()

- Primarily aimed at synchronization of time between hybrid simulations (multiple os-processes), snapshotting

- Using async\_update\_request, sc\_unsuspendable ()/sc\_suspendable() a b\_transport can be triggered from outside system (temporarily unblocking the simulation) → breaks Req. 3/4

## Other approaches

- B. Farkas, Standard Compliant Snapshotting for SystemC VPs, 2019

- Uses sc\_pause to enable the save\_state function, thereby ensuring that the event queue is empty

- The queue will be refilled upon restarting of the simulation and restoring the previous state of the attached models

- Mentions possibility of snapshotting based on certain events/conditions

- IEEE 1666-2011 Standard SystemC section 4.3.4.2

- Function sc\_pause shall cause the scheduler to cease execution at the end of the current delta cycle such that the scheduler can be resumed again later

- control is returned from sc\_start to sc\_main again

- sc\_start may be called again to resume simulation

- Note: sc\_start may only be called from within sc\_main

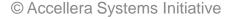

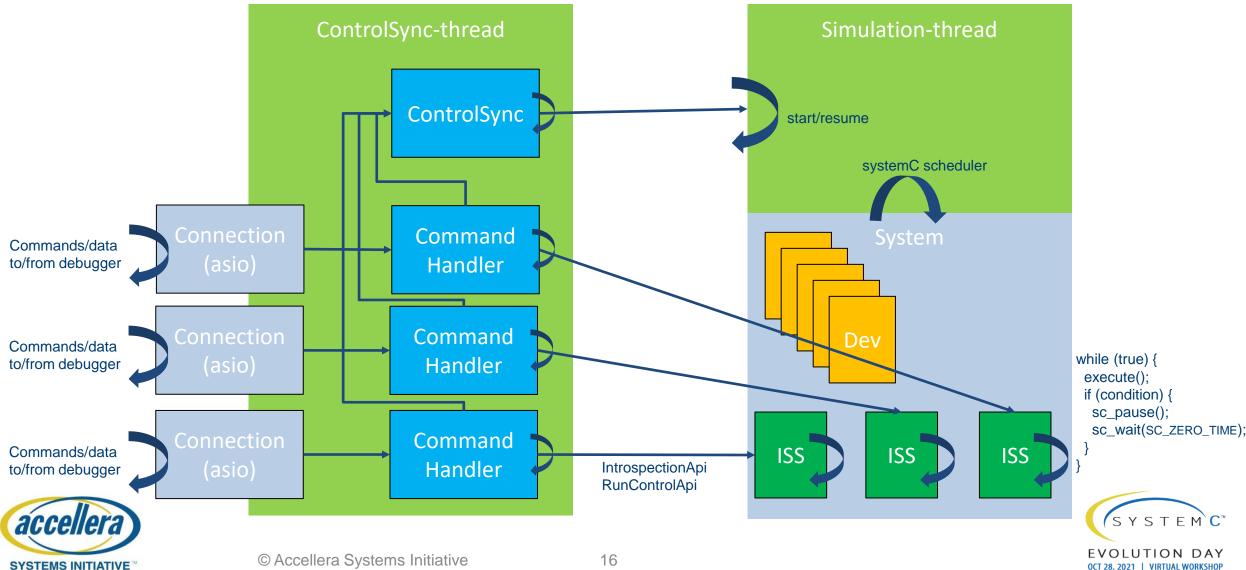

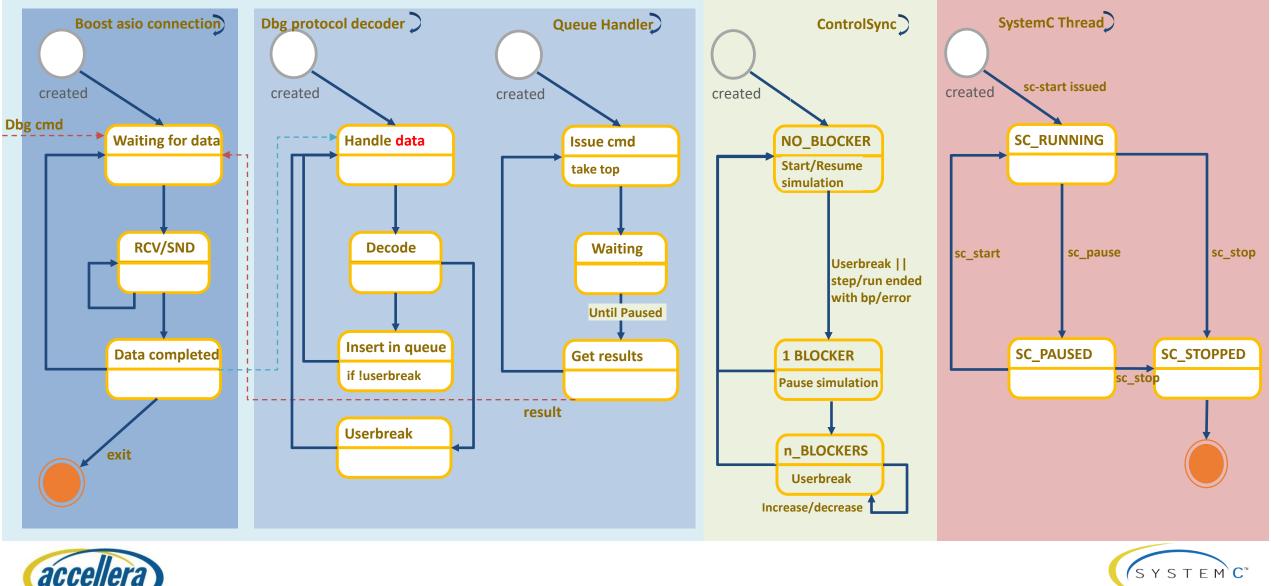

- Parallel SimulationControl-thread & Simulation-thread

- SimulationControl-thread uses boost::asio to handle one or more control-connections

- Use sc\_core::sc\_pause() to suspend simulation when required

- Call sc\_core::sc\_start() again to resume simulation Requires control of sc\_main implementation

- Simulation-thread is paused on condition in the target: interrupt/user-break/bp-hit

- Main loop in simulation-thread: simplified handling of pause/resume using 1 mutex/lock and 1 condition to interact with simulation-control thread

- When simulation-thread is paused & locked, new connections & user-break in other controlconnection are possible (since that does not require a reaction from the model anymore)

GREEN: major difference with previous solution

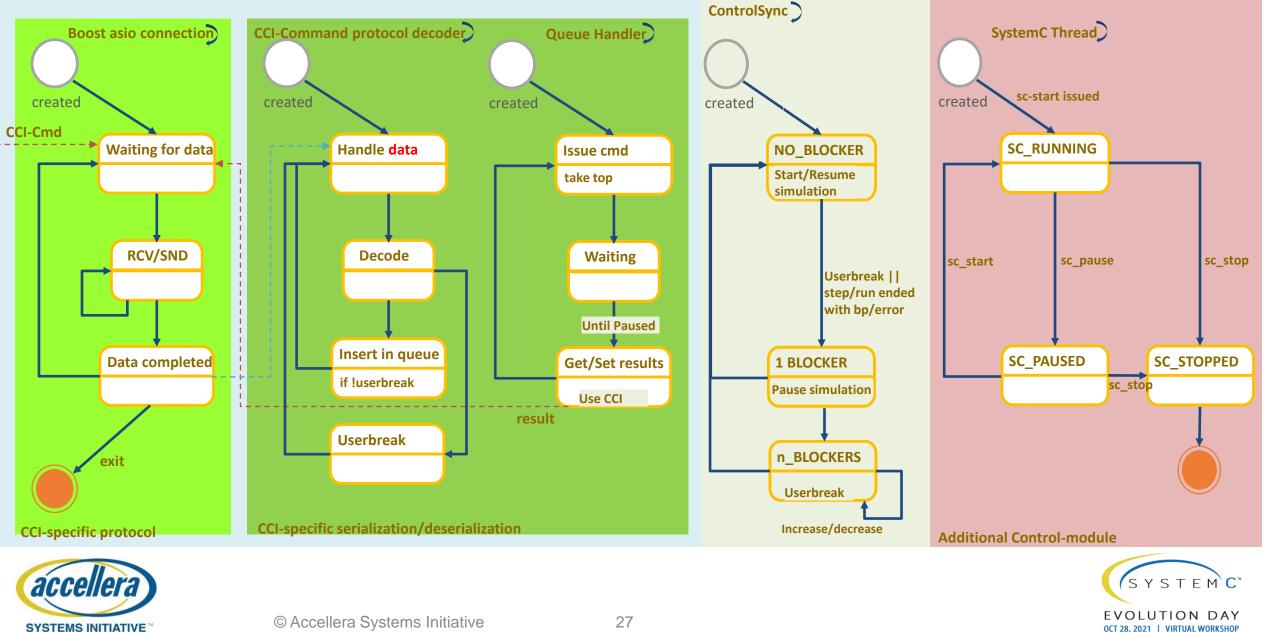

# Synchronization control

- SimulationControl-thread is responsible for

- #connections, #simulation\_blockers

- Increase #simulation\_blockers on attach/user-break,

- Pause (suspend) simulation on #simulation\_blockers == 1

controller will get correct response automatically

- If simulation was already paused (suspended)

→ create & send artificial 'interrupted'-response to debugger

- Decrease #simulation\_blockers on continue

resume simulation when #simulation\_blockers==0

SYSTEMS INITIATIVE

#### Code for sc\_main (replacement for sc\_start())

if (allowDebug) {

DebugService::getInstance().createMonitors(dbg\_port); // create the sessions std::thread debugService(debug\_task, &DebugService::getInstance().io\_service); debugService.detach(); // Do not block execution.

TLM global quantum

std::thread systemSimulation(simulation\_task, global\_quantum\_value); // calls sc\_start()

systemSimulation.join(); // wait until simulation finishes

if (allowDebug) {

debugService::getInstance().io\_service.stop(); // cleanup resources

#### Code for debug task

```

// The function we want to execute on the new thread.

void debug_task(boost::asio::io_service* io_service)

{

io_service->run();

}

```

Code for simulation task (simplified)

```

void simulation_task(uint64_t quantum_value) {

... /* Initialize the Global Quantum Keeper */

bool stopped(false);

while (!stopped) {

stopped = run_sim();

if (!stopped) {

// resume again if all controllers want to continue

ControlSync::instance().waitForCommand();

}

}

}

```

SYSTEMC<sup>™</sup> EVOLUTION DAY 0CT 28, 2021 | VIRTUAL WORKSHOP

Code for simulation task (simplified, without exception-handling)

/\* returns false for paused, true for stopped and/or error \*/

bool run\_sim() {

sc\_core::sc\_start();

ControlSync::instance().notifyControllers();

return (sc\_core::sc\_get\_status() != sc\_core::SC\_PAUSED);

}

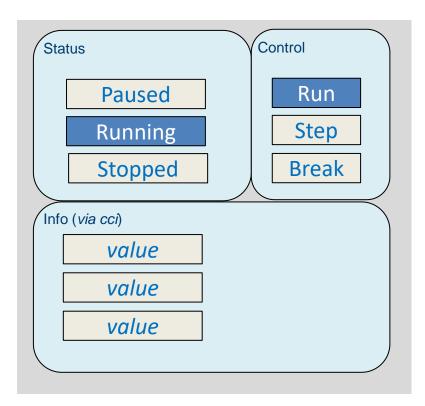

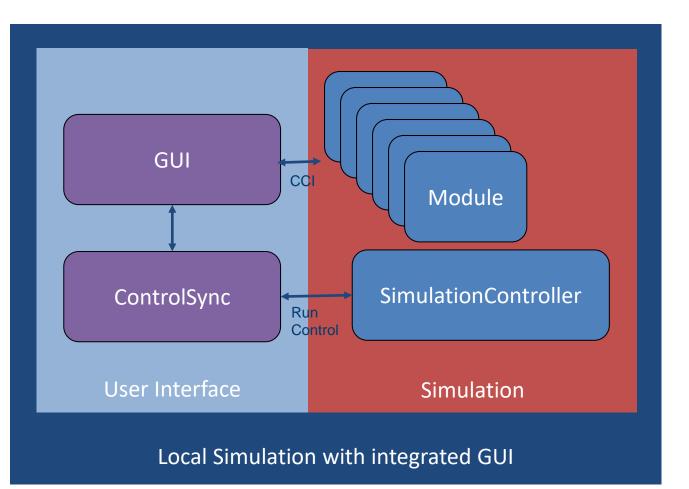

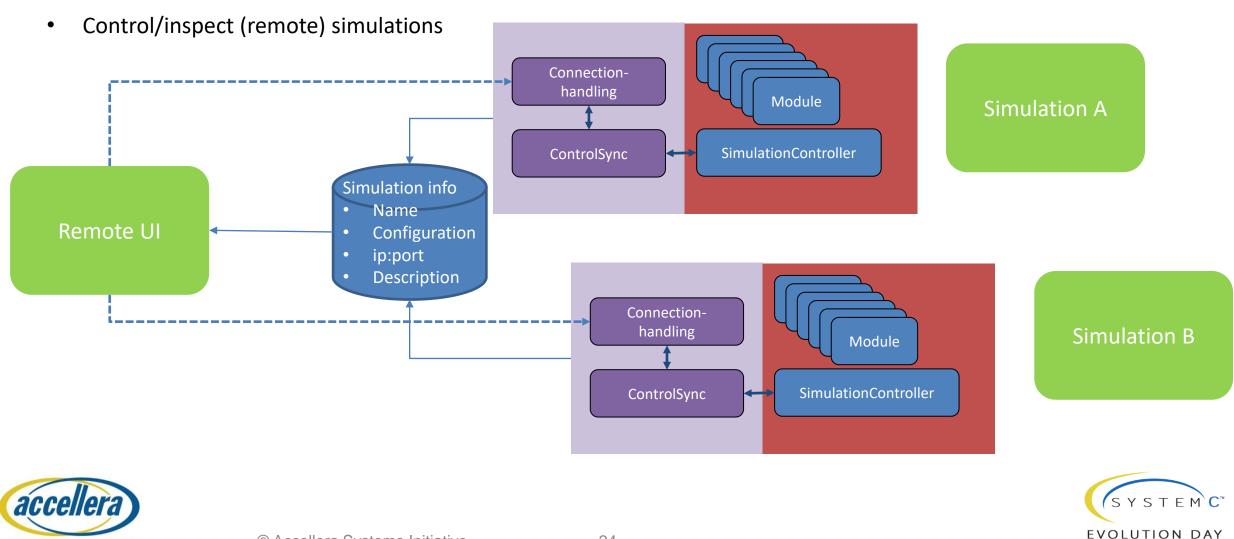

#### What if

- we use the previous concepts also for simulations without ISS-models?

- Generic system-simulation controller (api)

- Replace gdb rsp with remote-cci protocol (tbd)

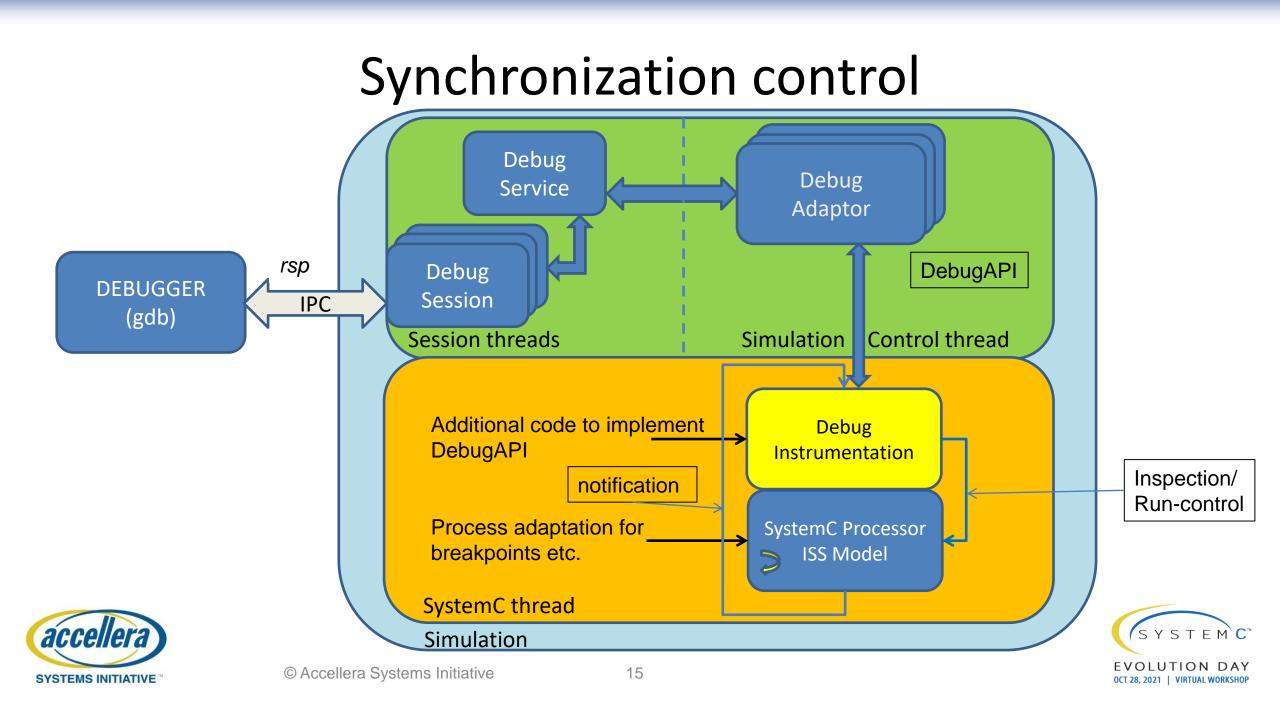

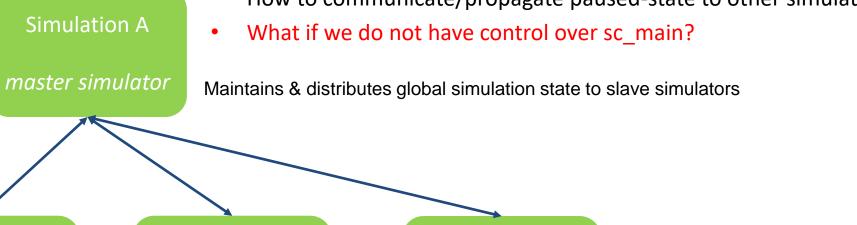

- we apply the same ideas to hybrid/distributed simulations?

- State-synchronization across multiple simulators

• Simple CCI/Control-GUI for simulation

SYSTEM C

ON

DAY

EVOLUTI

© Accellera Systems Initiative

SYSTEMS INITIATIVE

OCT 28, 2021 | VIRTUAL WORKSHOP

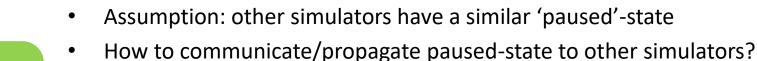

• SystemC-simulation combined with other simulator(s): hybrid/distributed simulation

Simulation B

slave simulator

Simulation C

slave simulator

Simulation D

slave simulator

Report local simulation state changes to master simulator Need specialized ControlSync instances in slaves to handle simulation state-control (only master can pause/resume)

### **Generic simulation-control**

### Generic simulation-control

Using generic SystemC-module implementing RunControlApi

```

class RunControlApi {

public:

/// constructor & destructor

RunControlApi() {};

~RunControlApi() {};

/// runcontrol

virtual void attachController()

= 0:

virtual void detachController() = 0;

virtual void step (const sc_core::sc_time& timeStep) = 0;

virtual void runUntilBreak()

= 0:

virtual void userBreak()

= 0; //< break current run/step

/// allow controller to inspect simulation before simulation end

virtual void endOfSimulationEvent() = 0;

};

```

### Generic simulation-control

```

void SimulationControl::main_thread() {

```

while (true) {

```

wait(m_attachEvent);

```

```

while (m_controller) {

```

```

if (m_stepping) wait(m_stepTime, m_detachEvent|m_userBreakEvent);

else wait(m_detachEvent|m_userBreakEvent);

```

```

if (m_controller) {

```

```

ControlSync::instance().controlBreak(this); sc_pause(); wait(SC_ZERO_TIME);

```

# Conclusion

- Current implementation (using sc\_pause-mechanism) implements all requirements under condition that:

- We have full control over sc\_main implementation

- No distributed/hybrid simulation scenarios are required

- In case a model is integrated by someone else, we cannot use this solution

- We have no control over sc\_main implementation, or it is not even used (running under direct control of the kernel, section 4.3.5 IEEE-SystemC) *Can we use sc\_pause in absence of sc\_start/sc\_main? It would seem not..*

- To become a full solution, we need some changes

# Proposal & Discussion

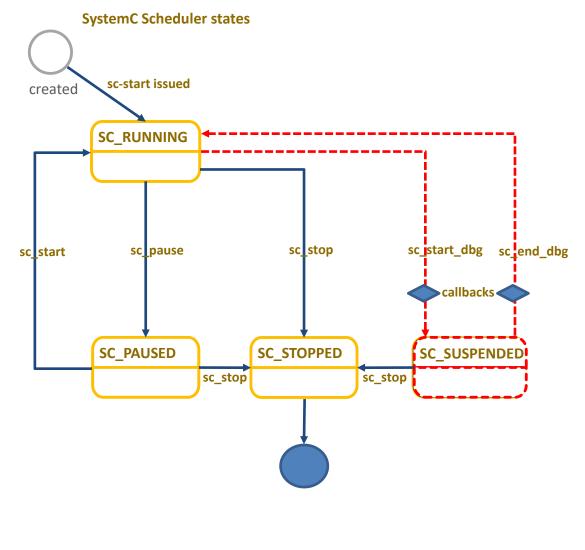

- Extend kernel scheduler state-machine with additional state SC\_SUSPENDED

- Like SC\_PAUSED, but does not return to sc\_main

- Enable callbacks on transitions to/from SC\_SUSPENDED to enable messaging to other simulators

- New api functions

- sc\_start\_debug()/sc\_end\_debug()

== sc\_suspend\_all()/sc\_unsuspend\_all with priority level

- Adapt implementation of ControlSync to use new api

- Similar way as proposed in '(Un)Suspend(able)') (patch merged 09/21/2021)

- Prepare patch

### **Proposal & Discussion**

© Accellera Systems Initiative