# The Intel<sup>®</sup> Simics<sup>®</sup> Simulator and SystemC\* and Threading

Jakob Engblom, Director of Simulation Technical Ecosystem jakob.engblom@intel.com

intel

## **Copyright Permission**

• A non-exclusive, irrevocable, royalty-free copyright permission is granted by **Intel** to use this material in developing all future revisions and editions of the resulting draft and approved Accellera Systems Initiative **SystemC** standard, and in derivative works based on the standard.

#### Legal Notice

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel, the Intel logo, and Simics are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others

© Intel Corporation.

# Designing Threading in the Simics<sup>®</sup> Simulator

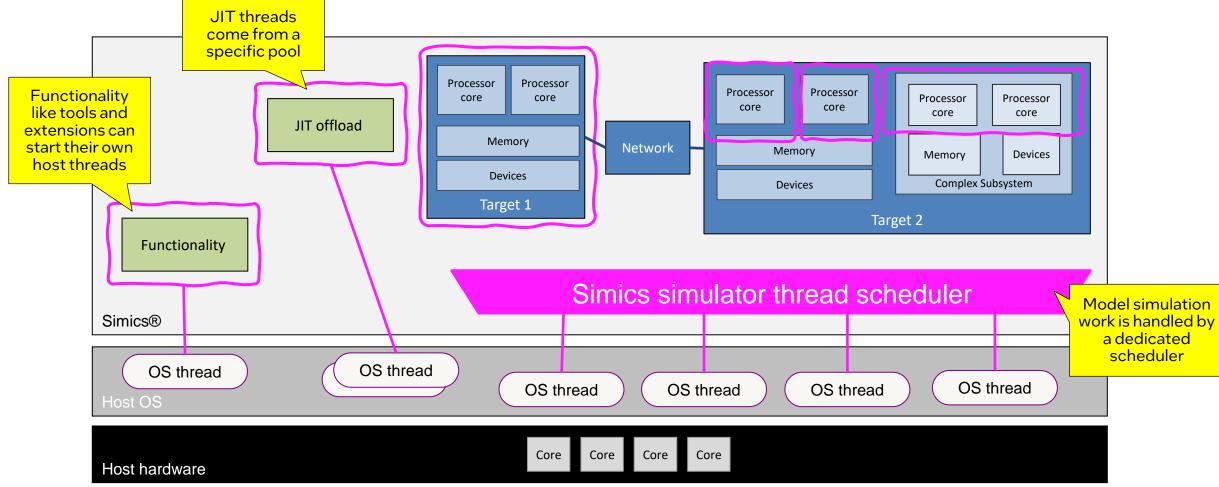

- Threading handled by the framework

- Defined host-independent threading semantics and threading execution modes

- User can enable/disable parallel execution

- Threading should affect as few modules as possible

- Fundamentally, parallel/concurrent coding is hard and should be isolated to a few places in the code base

- Device models should not need to change to enable threading – simplifies programming, simplifies deployment of threading

- In practice, most parallelism is provided by processors (and clocks), and a few features

- Revert to sequential execution on demand

- Support deterministic execution for software debug

- Support debug of models by removing threading as a complicating factor

- Losing determinism for performance is OK

- Fall back to slower deterministic mode if needed

- Advanced thread programming available

- Support advanced use cases where the standard threading solutions are insufficient

Threading should be easy and automatic for most modelers

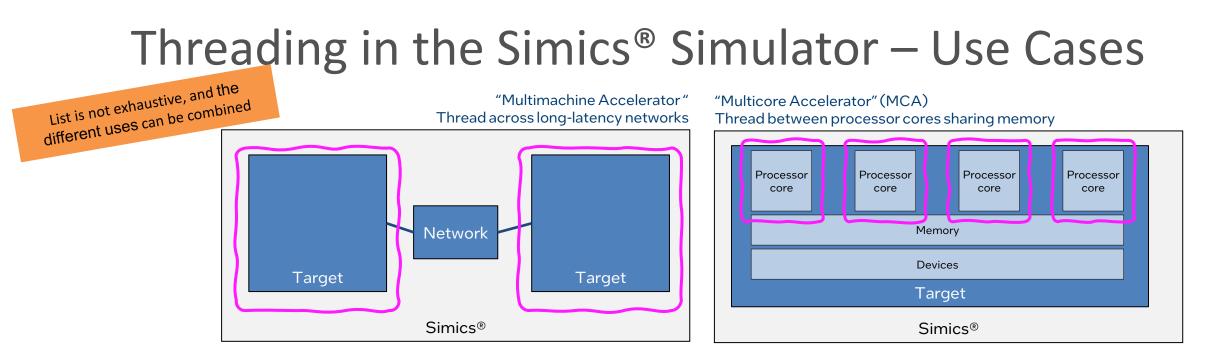

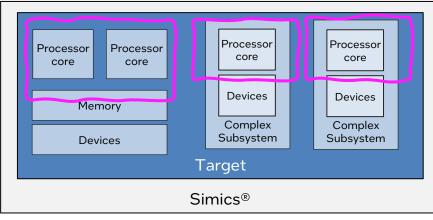

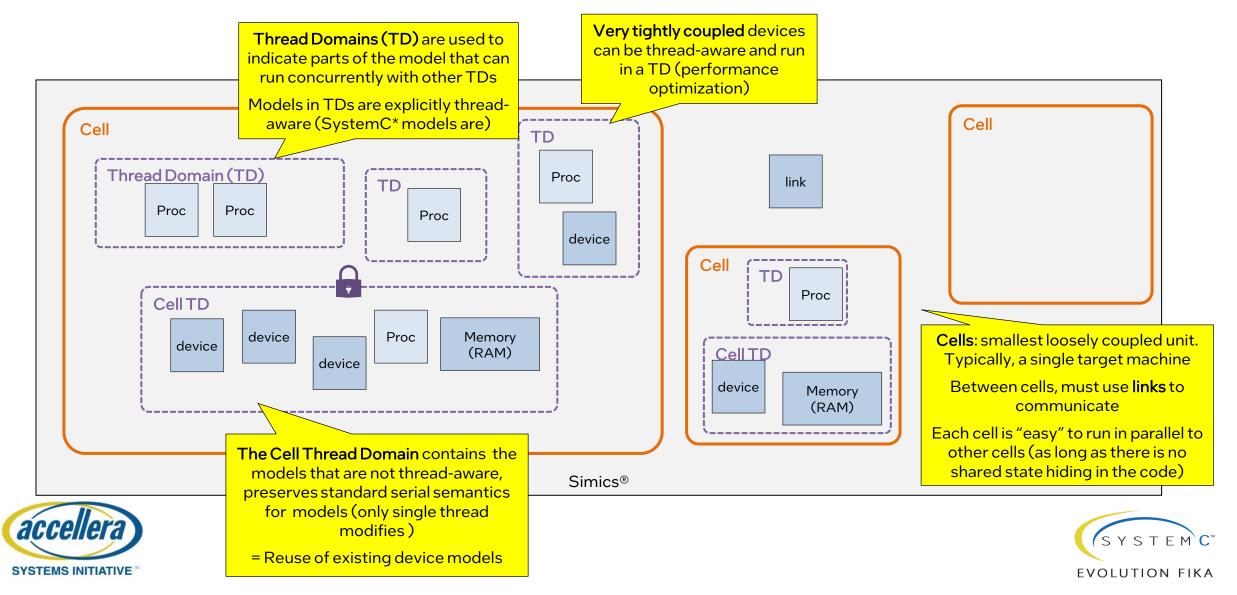

"Subsystem multithreading" Run separate (definition) subsystems on their own threads

Multithreading as coding pattern Use a thread to interact with the outside asynchronous world

#### How the Simics<sup>®</sup> Simulator uses Threads

### Simics<sup>®</sup> Simulator Threading Concepts

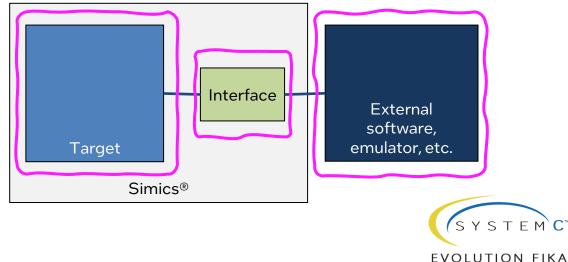

# SystemC\* Models in the Simics<sup>®</sup> Simulator

- Use Accellera\*-compliant SystemC models asis

- Including binary-compiled models

- ABI-compatibility required

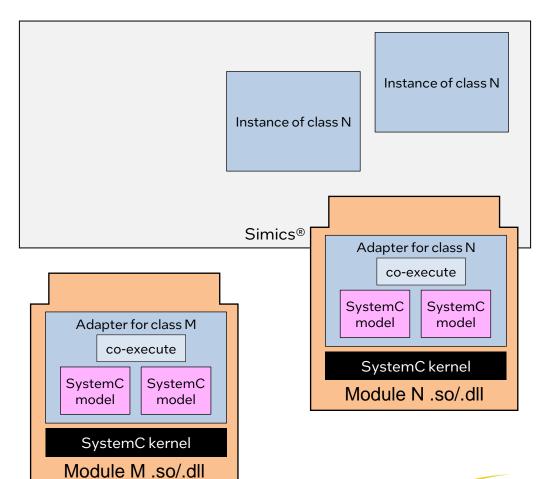

- SystemC models are compiled into/linked into a Simics module

- Each module can contain one or more top-level adapters

- Each adapter can be instantiated multiple times in the system model

- The adapter provides the interface between the SystemC subsystem and the Simics simulation environment

- The adapter provides a "co-execute" object that is scheduled by the Simics simulator core to run the model

- Modules are loaded dynamically when used

SYSTEMC<sup>™</sup> EVOLUTION FIKA \*Other names and brands may be claimed as the property of others

## Summary

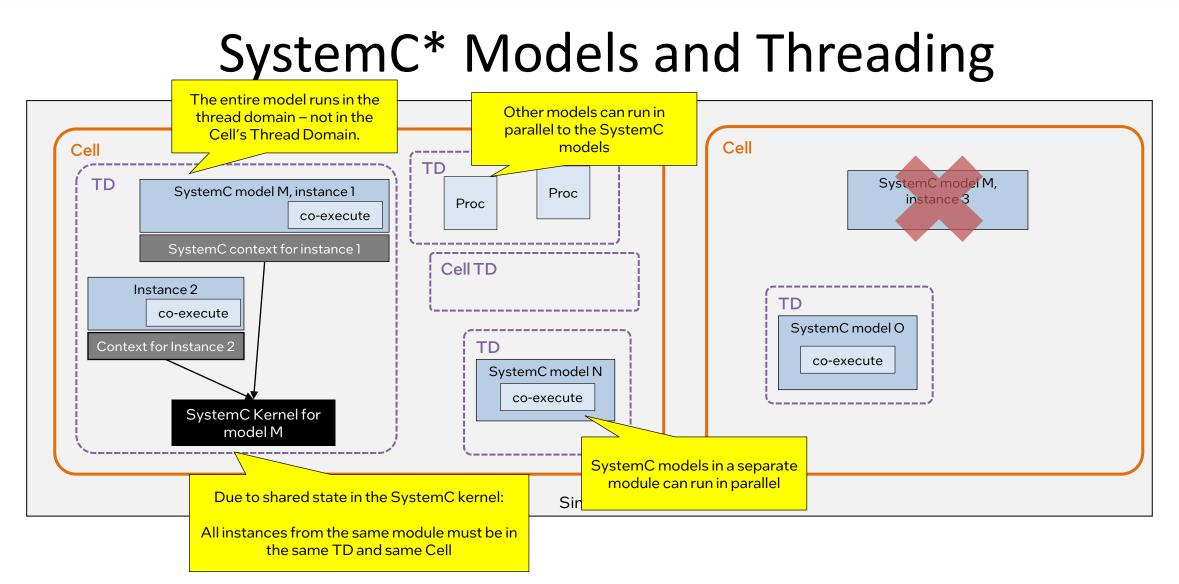

- The Simics<sup>®</sup> simulator can run multiple SystemC\* models in parallel to each other and to other Simics models

- Locking applied to accesses to shared state and devices, according to Simics API

- Parallelism is enabled using multiple separate kernels

- i.e., built on top, not inside of SystemC

- Semantics in each model is standard SystemC serial semantics

- Shared static state in the kernel limits available parallelism

- Fixing it requires an ABI change for the kernel

### More on the Simics<sup>®</sup> Simulator

- The Public Release of the Intel<sup>®</sup> Simics<sup>®</sup> Simulator

- Complete Simics base product

- Includes the Simics SystemC\* Library

- As well as Simics-native model builder tools

- Intel-based Quick-Start Platform

- Training materials and examples

- Bonus: the first release of Intel ISIM, the Intel Integrated Simulation Environment with Modeling, including examples of performance, power, and thermal models

https://developer.intel.com/simics-simulator

#### THE END