## SystemC Evolution Fika – 12 September 2023

#### Introduction

Mark Burton

Martin Barnasconi

systemc.org

systemc-evolution-fika@lists.accellera.org

# SystemC Evolution Fika - Agenda

| Time (CEST)   | Title                    | Presenter(s)                                                                          | Affiliation(s)                                                                               |

|---------------|--------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 16:00 - 16:10 | Welcome & Introduction   | Mark Burton <sup>1</sup> ,<br>Martin Barnasconi <sup>2</sup>                          | <sup>1</sup> Qualcomm,<br><sup>2</sup> NXP                                                   |

| 16:10 - 16:40 | SystemC IEEE 1666 update | Jérôme Cornet                                                                         | STMicroelectronics,<br>IEEE P1666 Chair                                                      |

| 16:40 - 17:10 | Tracing in SystemC       | Lukas Jünger <sup>1</sup> ,<br>Eyck Jentzsch <sup>2</sup> , Rocco Jonack <sup>2</sup> | <ul> <li><sup>1</sup> MachineWare GmbH,</li> <li><sup>2</sup> MINRES Technologies</li> </ul> |

| 17:10 - 17:30 | Q&A                      |                                                                                       |                                                                                              |

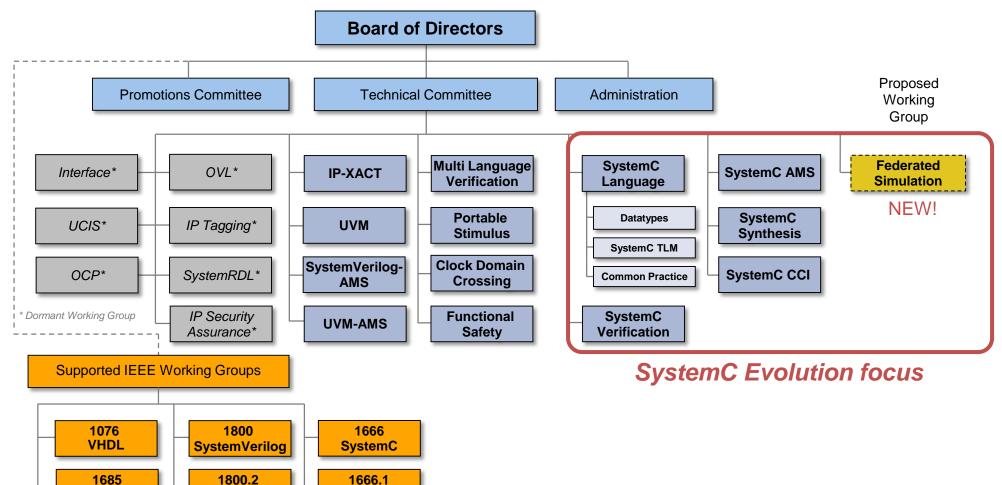

## Accellera SystemC Working Groups

**IP-XACT**

SystemC AMS

UVM

© Accellera Systems Initiative

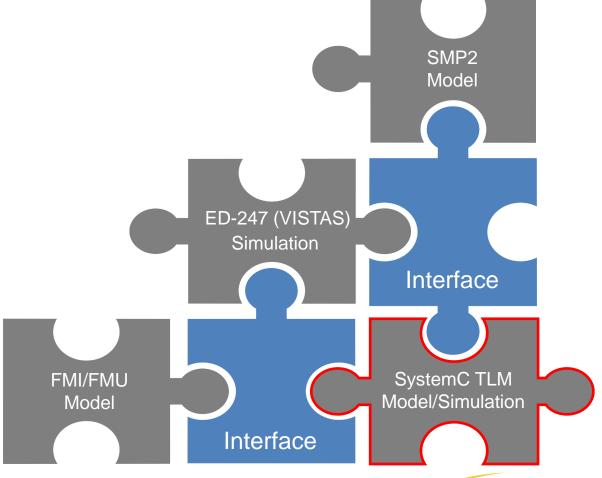

## Federated Simulation Standard (FSS)

Enabling cross-industry interoperability of simulation frameworks

- Objective: Cross-industry collaboration to improve the interoperability of product and environment simulation

- Approach: Leveraging and connecting existing standards and industry formats

- Introduce standardized interfaces

- Targeting a scalable simulation and modeling ecosystem, covering different levels of the 'OSI stack'

## FSS Proposed Working Group & First meeting

- Call for Participation is now open!

- PWG is open for everyone no Accellera membership required

- More information and PWG registration:

<a href="https://www.accellera.org/activities/proposed-working-groups">https://www.accellera.org/activities/proposed-working-groups</a>

- First in-person meeting **September 25+26, Toulouse, France**

- Day 1: Discuss industry use cases, requirements, applications

- Day 2: Organizational aspects incl alignment with other initiatives or organizations

- More information and event registration: <a href="https://evenium.events/8jxrclxh">https://evenium.events/8jxrclxh</a>

- Feel free to contact the organization committee for questions and additional information

- Martin Barnasconi, Mark Burton, Eric Jenn

## Next up – SystemC Evolution Day 2023

Mark your calendar

Date: 16 November 2023 (day after DVCon Europe 2023)

Time: 09:30 - 17:30 CET

Location: Holiday Inn Munich City Centre, Hochstrasse 3, 81669 Munich, Germany

- Call for Presentations still open

- Submit your ideas and contributions for additions and improvements to SystemC and/or its extensions covering TLM, CCI, AMS, Synthesis and/or Verification

- A contribution can be in the form of a finding, a result, or a proposal, but also a problem experienced that you feel needs attention and discussion in an Accellera and SystemC user-community context

- More information on the event and abstract submission process: <a href="https://systemc.org/events/sced2023/">https://systemc.org/events/sced2023/</a>

### systemc.org

#### Welcome to the SystemC Community Portal

Your online reference for everything related to SystemC, the language for system-level design, high-level synthesis, modeling and verification.

```

Overview

```

Downloads

```

#include <systemc>

#include "producer.h"

#include "consumer.h"

class top : public sc_core::sc_module

fifo fifo_inst{"Fifo1"};

producer prod_inst{"Producer1"};

consumer cons_inst{"Consumer1"};

top(sc core::sc module name name)

: sc_core::sc_module(name)

prod inst.out(fifo inst);

cons_inst.in(fifo_inst);

int sc_main (int, char *[]) {

top top1("Top1");

sc_core::sc_start();

return 0;

```