### SystemC Synthesis Workgroup Update

Frederic Doucet,Qualcomm,Mike Meredith,Cadence DeStuart Swan,Siemens ELMay 30th 2024Siemens EL

Qualcomm, Cadence Design Systems, Siemens EDA SWG chair SWG member SWG member

Workgroup introduction and overview of SystemC-based HLS (Fred)

Content of Current SWG Standard 1.4.7 (Mike)

Overview of important items for standardization (Stuart)

Summary and Call for participation (Fred)

# SystemC Synthesis Workgroup

#### Workgroup objectives:

- 1. Define synthesizable subset and consistent modeling style for SystemC HLS

- 2. Streamline SystemC HLS syntax and semantics to

- a) achieve interoperability between HLS/HLV tool,

- b) help standardize HLS/HLV design flows and trainings to be tool independent, and

#### Current public standard: <u>1.4.7</u>

- Workgroup re-starting with focus on new items

#### Standardization process

- 1. Members list, discuss and agree on candidate items for standardization

- 2. Design Objective Document (DOD) documents work items for standardization

- 3. Open call for contributions from workgroup members for DOD work items

- 4. WG members to submit contributions for specific item

- a) WG discusses contribution, works with contributor on any requested changes, and

- b) votes for inclusion in standards document and collateral (PoC / test code etc)

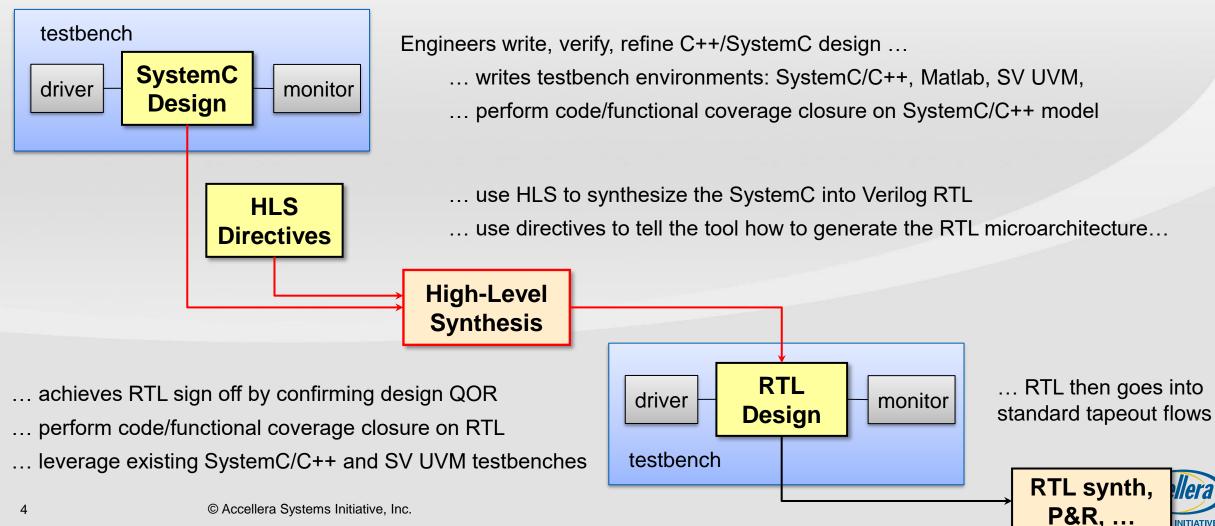

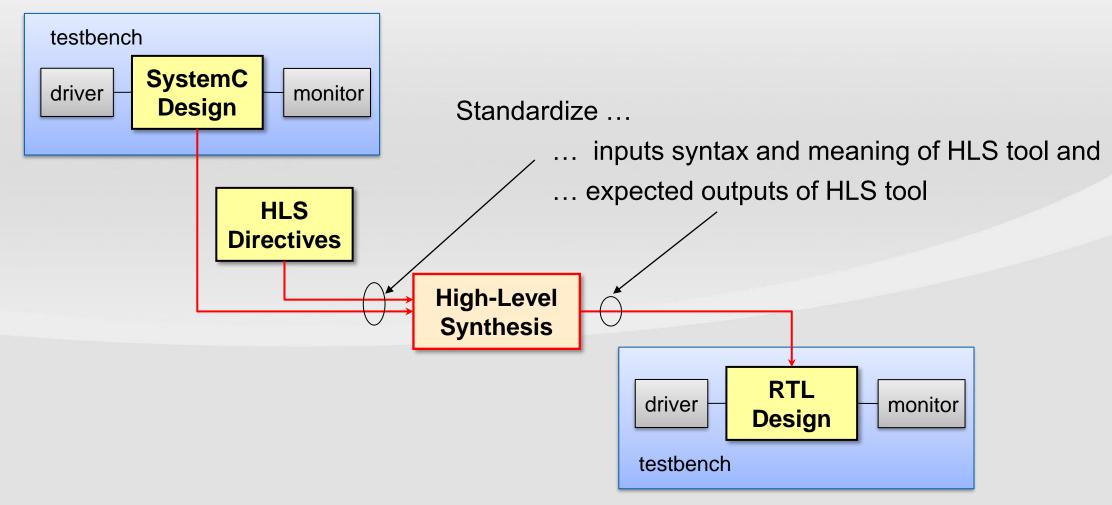

# **Typical SystemC High-level Synthesis Flow**

## Focus of SystemC Synthesis Standard Workgroup

| Workgroup introduction and overview of SystemC-based HLS | (Fred)   |

|----------------------------------------------------------|----------|

| Content of Current SWG Standard 1.4.7                    | (Mike)   |

| Overview of important items for standardization          | (Stuart) |

| Sumary and Call for participation                        | (Fred)   |

### Scope of Current SystemC Synthesizable Subset Standard

#### Current standard is version 1.4.7

#### Objectives for the 1.4.7 standard

- Define a meaningful minimum subset

- Establish a baseline for transportability of code between HLS tools

- Leave open the option for vendors to implement larger subsets and still be compliant

- Include useful C++ semantics, if they can be known statically eg templates

- Covers behavioral model in SystemC for synthesis

- Covers RTL model in SystemC for synthesis

### Elements of the 1.4.7 standard

### SystemC Elements

- Modules

- Processes

- SC\_CTHREAD

- SC\_THREAD

- SC\_METHOD

- Reset

- Signals, ports, exports

- SystemC datatypes

### C++ Elements

- C++ datatypes

- Expressions

- Functions

- Statements

- Namespaces

- Classes

- Overloading

- Templates

### SystemC Synthesizable Subset Standard 1.4.7 Hardware structure

=> Syntax to provide hardware-meaning to C++

- Modules

- Signal ports

- Signal connections

- Processes

- Wait statements

$a \xrightarrow{\text{clk}} DUT$   $a \xrightarrow{\text{b}} DUT$   $a \xrightarrow{\text{clk}} Z$

HLS tool strictly follows the syntax to transform SystemC into Verilog

```

1: SC MODULE(DUT) {

sc_in <bool> SC_NAMED(clk);

2:

sc in <bool> SC NAMED(nrst);

3:

4:

5:

sc_in <sc_int<12>> SC_NAMED(a);

sc in <sc int<12>> SC NAMED(b);

6:

7:

sc_in <sc_int<12>> SC_NAMED(c);

8:

sc_in <sc_int<12>> SC_NAMED(d);

9:

sc_out<sc_int<24>> SC_NAMED(z);

10:

SC CTOR(DUT) {

11:

SC THREAD(proc);

12:

13:

sensitive << clk.pos();</pre>

14:

reset signal is(rst n, false);

15:

16:

17:

void process() {

18:

z = 0;

19:

wait();

20:

21:

while (true) {

22:

auto v1 = a * b;

23:

auto v2 = c * d;

24:

auto v3 = v1 + v2;

25:

wait();

26:

z = (v3>>1);

27:

28:

29: };

```

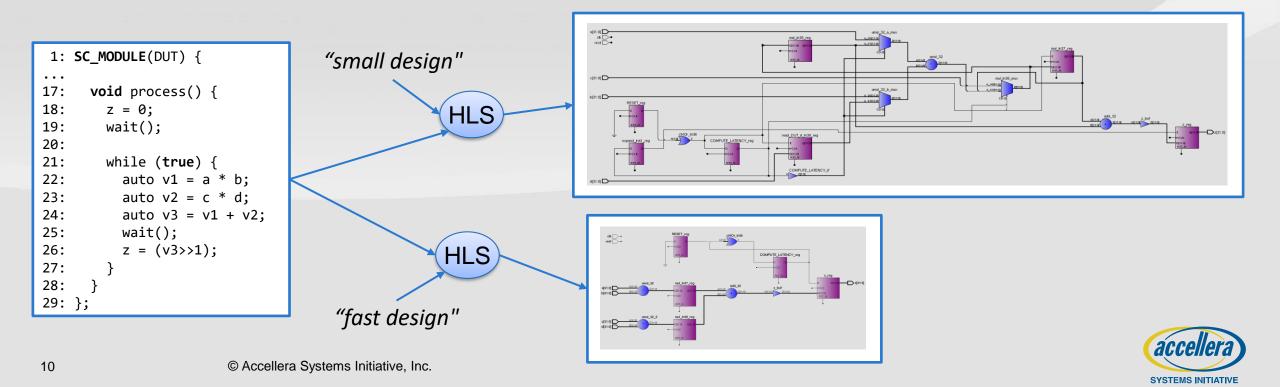

# Not in current Standard: HLS Directives

#### Instructs the HLS tool how to generate the micro-architecture

- Impacts latency, resources, registers, multiplexers, FSM, etc.

- They are as important to the design as the source code

- Subject of standardization activities

Workgroup introduction and overview of SystemC-based HLS (Fred) Content of Current SWG Standard 1.4.7 (Mike) > Overview of important items for standardization (Fred) Summary and Call for participation

# **Key HLS Directives**

Some C++ constructs can interpreted in a variety of ways when synthesizing SystemC into RTL

#### ➔ Array implementation

- Memory, register file, registers

- ➔ Loop implementation

- Unrolling, pipelining, merging, etc.

```

sc_int<12> data[N];

sc_int<12> coeffs[N];

...

MAC_H: for (int i=0;i<N;i++) {

acc += data[i] * coeffs[i];

}

```

#### Custom resources

- Larger resources that can be used by the scheduler

- Arithmetic optimizations cluster for coarser grain resource sharing

- Multicycle operations

#### → Scheduling

- Latency/throughput constraints:

- where/when to add states

- Protocol constraints :

- Where/how to access I/O

### **Channels and Memory Architecture**

- Channel-based I/O can be implemented as SystemC IP

- Can implement TLM and PIN-level semantics

- Presents TLM API to the design

- Memories can be modeled as

- SystemC IP

- Shown here

- C++ Arrays

- Standardization of channels and memory libraries and IP is a topic of planned work

- Exact syntax specifics will be discussed

| 1:  | <pre>SC_MODULE(MatrixMultiply) {</pre>                                                      |

|-----|---------------------------------------------------------------------------------------------|

| 2:  | <pre>sc_in<bool> SC_NAMED(clk) ;</bool></pre>                                               |

| 3:  | <pre>sc_in<bool> SC_NAMED(rstn);</bool></pre>                                               |

| 4:  | TLM                                                                                         |

| 5:  | Connections::In <sc_int<8>&gt; SC_NAMED(A); Channels</sc_int<8>                             |

| 6:  | Connections::In <sc_int<8>&gt; SC_NAMED(B);</sc_int<8>                                      |

| 7:  | Connections::Out <sc_int<8+8+3>&gt; SC_NAMED(C);</sc_int<8+8+3>                             |

| 8:  | Connections::SyncChannel SC_NAMED(sync);                                                    |

| 9:  |                                                                                             |

| 10: | <pre>shared_bank_array<sc_int<8>, 8, 8*2&gt; SC_NAMED(B_transpose);</sc_int<8></pre>        |

| 11: | Connections::Combinational <array_t<sc_int<8>,8&gt;&gt; SC_NAMED(A_row);</array_t<sc_int<8> |

| 12: |                                                                                             |

| 13: | SC_CTOR(matrixMultiply) {                                                                   |

| 14: | SC_THREAD(pack_A);                                                                          |

| 15: | sensitive << clk.pos(); Memory                                                              |

| 16: | async_reset_signal_is(rstn, false); Models                                                  |

| 17: |                                                                                             |

| 18: | SC_THREAD(transpose);                                                                       |

| 19: | <pre>sensitive &lt;&lt; clk.pos();</pre>                                                    |

| 20: | async_reset_signal_is(rstn, <b>false</b> );                                                 |

| 21: |                                                                                             |

| 22: | <pre>SC_THREAD(mac);</pre>                                                                  |

| 23: | <pre>sensitive &lt;&lt; clk.pos ();</pre>                                                   |

| 24: | <pre>async_reset_signal_is(rstn, false);</pre>                                              |

| 25: | }                                                                                           |

|     |                                                                                             |

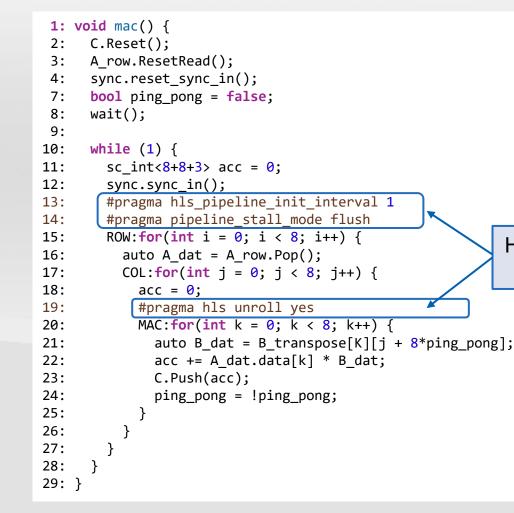

### **Directives for Loop Unrolling and Pipelining**

#### Many forms of directives can be considered

- Pragmas or other annotations in the source code

- Shown here

- External, e.g. Tcl control

- Standardizing one or more approaches is a topic of planned work

HLS Directives specified using inlined pragmas

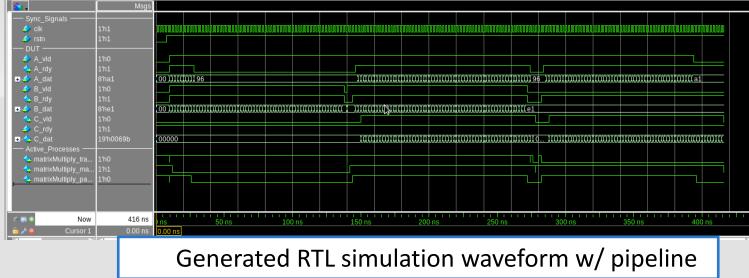

# **Loop Pipelining: Throughput and Latency**

- HLS users need the ability to do accurate performance analysis on the pre-HLS model

- Much better than on RTL

- HLS tool will increase design latency when pipelining a loop, for a specified throughput

- ... to meet timing or reduce area

- Use of channels with handshake makes design robust to such changes

- These channels need to be standardized

Workgroup introduction and overview of SystemC-based HLS (Fred)

Content of Current SWG Standard 1.4.7 (Mike)

Overview of important items for standardization (Stuart)

Summary and Call for participation (Fred)

# **HLS Standardization Topics**

#### **1.** Syntax and semantic interpretation

- Unambiguous interpretation SystemC syntax for synthesis

- Structure and Interfaces: modules, ports

- Behavior descriptions: methods, threads and wait()

- Scheduling rules (where states are added, how are I/O kept together etc.)

- Expected syntax for HLS-generated output

#### 2. HLS Directives

- loops (pipelining, unrolling etc.), arrays and memories, input and output scheduling, specification of latency and throughput constraints, etc

#### 3. Communication interfaces

- Channels (point-to-point, fifos, message passing) and memory-like constructs (banks, sram)

# **HLS Standardization Topics**

#### 4. Modern language constructs

- Which C++17/C++20 language constructs to be supported for HLS

- Which standard library classes (std::\*) to be supported for HLS

#### **5.** Synthesizable Data types

- Float, complex, arrays, fixed-point, composite data types support (arrays, structs, complex data type)

- How to we synthesize arrays, structs and other abstract collections to different storage types

- Standalone header files for all synthesizable datatypes.

#### 6. SOC/infrastructure libraries and common design basic blocks

#### 7. Proof-of-concept implementation and examples

- To drive the success, discuss a code tarball documenting the standard with:

- Regression suite : qualify the syntax works the way as expected, and

- Set of examples: more educational, demonstrating the standard modeling style

# **Call for participation**

#### Join the workgroup !

- https://www.accellera.org/activities/working-groups/systemc-synthesis

- https://workspace.accellera.org/wg/SWG/dashboard

- Meeting schedule:

- On the 2nd Wednesday of every month

- 8:00 AM 9:30 AM PDT / 17:00 18:30 CET

### Thank you for listening!